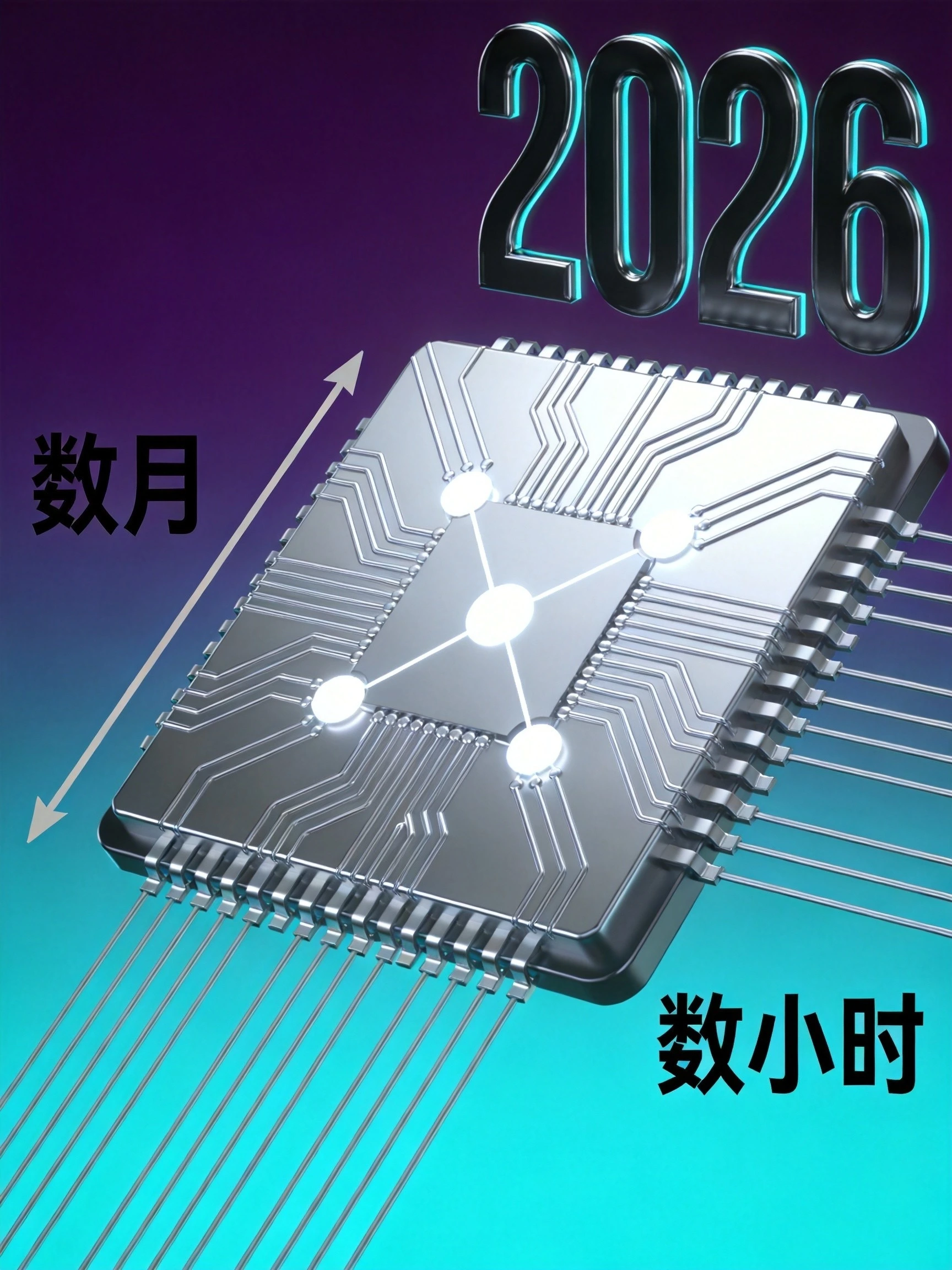

一、震撼业界的数字:10个月到1夜

2026年4月,一组数据在半导体圈引发热议:

英伟达透露,其最新一代Blackwell架构芯片的设计过程中,AI系统承担了大量工作。某些模块的设计周期从传统的10个月压缩到了1个夜晚。

10个月 vs 1夜——这个对比足够震撼。

要知道,传统芯片设计是一项极其复杂的系统工程。以一颗中等复杂度的SoC为例,设计周期通常需要12-18个月,涉及数千名工程师、数百个设计模块、数十亿个晶体管。

设计流程包括:架构定义、前端设计(RTL编码)、后端设计(布局布线)、仿真验证、时序分析、功耗优化……每个环节都可能反复迭代,每次迭代都意味着时间和成本的消耗。

而英伟达的实践表明,当AI深度介入这个过程时,效率提升是数量级的。

二、AI设计芯片的三个层次

要理解英伟达的做法,首先要搞清楚”AI设计芯片”到底意味着什么。

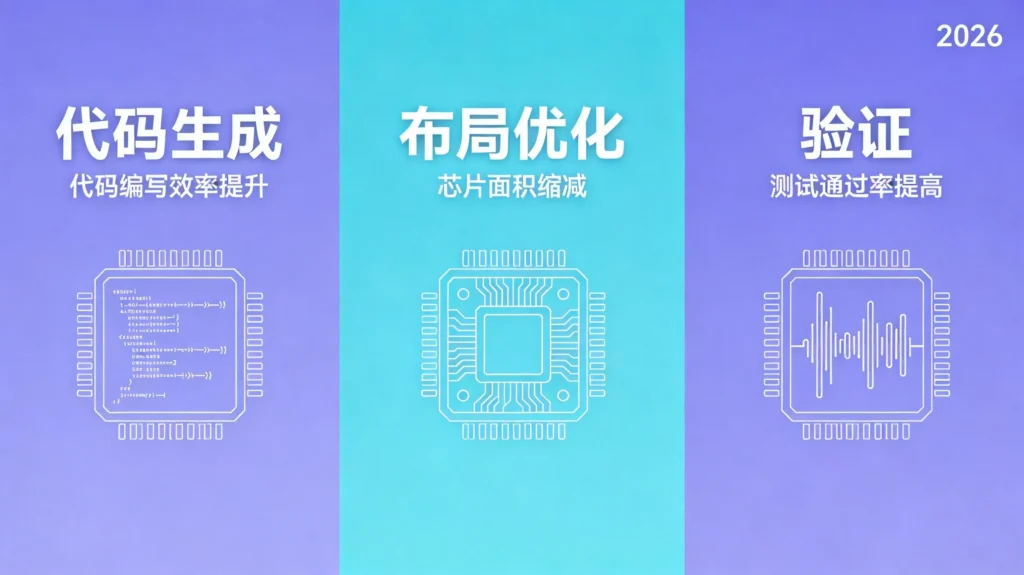

这个过程可以分为三个层次:

层次一:代码生成

这是最基础也是最成熟的应用。

AI可以自动生成RTL代码(寄存器传输级代码),将高层规格描述转换为可综合的硬件描述语言。传统方式下,工程师需要手动编写Verilog或VHDL代码;现在,AI可以根据自然语言描述或规格文档,自动生成符合要求的代码。

英伟达的内部工具已经可以处理大部分”标准化”的设计模块——接口控制器、时钟管理单元、基础运算单元等。工程师的角色从”写代码”变成了”审代码”。

层次二:布局布线优化

芯片的物理设计(布局布线)是另一个耗时大户。

传统的EDA工具需要工程师手动设置大量约束条件,然后由工具进行优化。但AI的介入让这个过程变得更加”智能”。

基于强化学习的方法可以自动探索设计空间,找到更优的布局方案。AI可以同时考虑时序、功耗、面积、散热等多个维度,进行全局优化。

有数据显示,在某些关键模块上,AI辅助的布局方案比纯人工方案节省15%的面积,同时降低20%的功耗。

层次三:验证与调试

芯片验证是设计周期中最耗时的环节之一,通常占整个设计周期的60%-70%。

AI在验证中的应用主要体现在两个方面:

自动生成测试向量:AI可以根据设计规格自动生成覆盖率高、针对性强的测试用例,减少遗漏。

智能缺陷定位:当仿真失败时,AI可以快速定位问题根源,将调试时间从数天缩短到数小时。

英伟达的实践表明,AI可以将整体验证效率提升3-5倍。

三、为什么是英伟达

在全球范围内,为何是英伟达率先实现了AI设计芯片的规模化应用?

第一,海量内部需求。

英伟达每年推出的新芯片数量众多,GPU、CPU、DPU、SoC……每个产品线都在快速迭代。这种压力倒逼英伟达必须找到效率提升的方法。

第二,自家GPU的算力优势。

英伟达可以用自己的GPU训练设计AI,然后用这些AI来设计下一代GPU。这种”飞轮效应”让英伟达在AI应用上具有天然优势。

第三,数据积累深厚。

过去几十年积累的芯片设计数据,是训练AI模型的最佳语料。英伟达拥有全球最丰富的芯片设计数据库之一。

第四,软硬件协同优化。

英伟达的CUDA生态和配套软件工具链,为AI设计工具的开发和部署提供了完善的基础设施。

这形成了一个正向循环:AI设计出更好的芯片→更好的芯片提供更多算力→更多算力训练更强的AI→更强的AI设计更好的芯片。

四、EDA厂商的焦虑与转型

英伟达的实践,对传统EDA厂商形成了直接压力。

Cadence、Synopsys、Mentor(现西门子EDA)是全球EDA市场的三大巨头,长期以来垄断了芯片设计工具市场。但AI的崛起,正在动摇它们的地位。

Cadence的应对是将AI深度整合进自家工具链。其 Cerebrus 产品主打”智能芯片设计”,可以在后端布局布线环节实现自动化优化。官方数据显示,使用Cerebrus后,设计效率提升40%。

Synopsys则押注于”AI-first”架构。其 PrimeSim 系列引入了AI加速的仿真引擎,将验证速度提升10倍以上。同时,Synopsys还在探索用大模型直接生成RTL代码的可能性。

新势力也在入局。 一些初创公司正在开发”AI-native”的芯片设计工具,试图绕过传统EDA的架构限制,用全新的方法论重新定义芯片设计流程。

五、芯片设计师的角色转变

AI介入芯片设计,对从业者意味着什么?

一个显而易见的担忧是:芯片设计师会不会失业?

这个问题的答案,或许要分短期和长期来看。

短期内,AI不会取代人,而是放大人的能力。

一个会用AI工具的初级工程师,生产效率可以超过不会用AI的高级工程师。这意味着”会用AI”将成为芯片设计岗位的基本技能要求。

中期来看,岗位结构会发生调整。

传统的”RTL编码”、”布局布线”等操作性岗位需求会减少,而”架构设计”、”系统优化”、”AI模型训练”等高阶岗位需求会增加。

工程师需要具备跨学科能力:既懂芯片设计,又懂AI应用;既能设定设计目标,又能评估AI输出。

长期来看,行业门槛可能会下降。

当AI能够承担大部分”标准化”设计工作后,芯片设计可能会变得更加”民主化”。更多中小企业甚至初创公司,也能够负担得起芯片设计成本。

这将催生新一轮的芯片创新浪潮——就像大模型降低了AI应用的门槛,AI设计工具也将降低芯片创新的门槛。

六、技术挑战与局限

尽管前景光明,但AI设计芯片仍面临诸多挑战。

第一,生成质量的不确定性。

AI生成的代码或布局方案,可能存在难以预料的缺陷。虽然可以通过仿真验证来兜底,但”AI幻觉”问题在芯片设计中同样存在——AI可能生成看似合理但实际上有问题的设计方案。

第二,专利与版权争议。

当AI生成的芯片设计与现有专利高度相似时,责任归属如何界定?这涉及复杂的知识产权问题,目前尚无明确答案。

第三,安全风险。

芯片设计是信息安全的核心环节。如果AI模型被恶意攻击或植入后门,后果不堪设想。如何保证AI设计工具的安全性,是一个严肃的课题。

第四,复杂系统的局限性。

对于高度复杂、需要跨模块协调的设计,当前的AI工具仍有局限。AI更适合处理”边界清晰”的子模块,而非”全局统筹”的系统架构。

七、产业影响:从芯片设计到AI闭环

英伟达用AI设计芯片的实践,其意义远超”提高效率”本身。

它代表了一种全新的思路:用AI来加速AI的进化。

英伟达Blackwell芯片的成功,证明了这套方法的可行性。更强的GPU带来了更强的AI,更强的AI又设计出更强的GPU——这个飞轮正在加速旋转。

对整个行业而言,这提供了一个重要启示:在AI时代,企业最重要的资产不是某一款产品,而是持续迭代的能力。

谁能建立更高效的AI应用闭环,谁就能在未来的竞争中占据优势。

八、结语:工具改变世界

回顾人类技术史,每一次重大的效率革命,都伴随着工具的革新。

蒸汽机改变了体力劳动的效率,计算机改变了信息处理的效率,而AI正在改变知识工作的效率。

芯片设计是知识工作最密集的领域之一。当AI能够在这个领域实现数量级的效率提升时,它预示着一个更大的变革正在到来。

未来的芯片,可能不再由人类单独设计,而是由人类和AI共同完成。人类负责定义问题、设定目标、评估结果;AI负责执行细节、探索方案、优化细节。

这不是”人类vs AI”的竞争,而是”人类+ AI”的协作。

就像CAD软件改变了工程制图,AI正在改变芯片设计。而每一次工具的革新,都会催生新的可能。

10个月到1夜,这个数字或许只是一个开始。

相关阅读:

发表回复